반도체 트랜지스터의 집적도는 18개월마다 2배가 된다는 '무어의 법칙'을 IBM이 깨뜨릴 수도 있을 것으로 보인다.

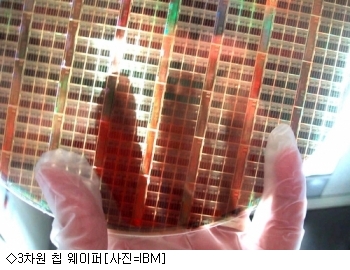

미국 IBM은 17일(현지시각) 뉴욕주 요크타운에 위치한 왓슨연구소에서 차세대 컴퓨터 칩셋 제조 기술인 '3차원 집적' 기술을 개발하고 있다고 발표했다.

이같은 3차원 반도체 집적 시도는 하이닉스와 같은 메모리 반도체 업체에서 일부 시도된 적은 있지만 컴퓨터 프로세서와 같은 비메모리 반도체 부문에서 상용화 연구를 진행한 것은 IBM이 가장 빠르다.

◆평면 아닌 3차원으로 반도체 집적

연산 능력을 가진 컴퓨터 프로세싱 반도체는 하나의 실리콘 다이에 얼마나 많은 '트랜지스터'가 집적되느냐에 따라 연산 능력이 좌우된다.

세계 최대 반도체 업체인 인텔의 창립자 고든 무어는 매 18개월마다 이 트랜지스터의 집적도가 2배가 된다는 유명한 '무어의 법칙'을 발표했다.

인텔은 현재까지는 90나노미터, 65나노미터, 45나노미터 등으로 미세공정을 적용해 이를 실현해왔다. 실제 가장 최근에 발표된 인텔 아이테니엄 컴퓨터 칩셋에는 하나의 실리콘 다이에 2억개의 트랜지스터가 집적돼 있다.

하지만 향후 예정돼 있는 32나노미터 초미세 공정 이후에는 사실상 트랜지스터 집적도를 물리적으로 더 이상 높이기가 힘들어, 2012년 이후에 무어의 법칙이 깨지는 것 아니냐는 우려도 일각에서는 제기되고 있는 상황.

더구나 전력 소모량과 발열문제 때문에 컴퓨터 프로세서 칩셋의 '크기'가 지속적으로 줄어들고 있는 상황에서 트랜지스터 집적도를 높이는 문제는 인텔 뿐만아니라 컴퓨터 반도체 업계 전체의 숙제가 되고 있다.

이런 시점에서 또 다른 컴퓨터 프로세서 제조업체 IBM이 반도체 집적도 한계를 깨뜨릴 수 있는 기술을 연구하고 있는 중이라고 밝힌 것이다.

왓슨연구소의 컴퓨터 기술연구 담당 류경동 박사는 "IBM이 개발하고 있는 3차원 통합(3D Integration) 기술은 실리콘을 위아래로 '쌓아' 하나의 칩셋 내 트랜지스터 집적도를 몇배 이상 높일 수 있도록 하는 기술"이라고 설명했다.

이는 비단 트랜지스터 집적도 뿐만 아니라 하나의 칩셋 내에서 CPU와 메모리 등이 '계층'을 이루고 위아래로 '통신' 할 수 있도록 함으로써 전체적인 시스템 성능을 크게 높일 수 있다는 게 류 박사의 설명이다.

◆발열 현상은 '공기방울'이 해결

위아래로 반도체를 집적하는 3차원 통합 기술은 반도체 업계에서는 금기시 되는 일이다. 반도체가 작고 트랜지스터 갯수가 많을수록 데이터를 처리하면서 발생하는 열이 높아 오류를 일으킬 가능성이 높기 때문이다.

하지만 IBM 측은 이 발열 문제를 고유의 '공기 방울' 기술로 해결할 수 있었다고 설명했다.

IBM 시스템 부문 스티브 샘즈 부사장은 "윗층과 아랫층 반도체 사이에 일종의 공기방울로 구성된 '버퍼'를 둬 반도체에서 나오는 열을 빠르게 식히고, 상호 열간섭 현상도 없앨 수 있었다"고 설명했다.

샘즈 부사장은 "바로 이 기술이 타 반도체 업체가 따라올 수 없는 IBM의 기술 우위"라는 점도 강조했다.

IBM이 현재 연구 중인 이 3차원 반도체 통합 기술은 ▲위아래로 반도체를 집적하는 부분 ▲공기방울을 이용한 발열 해결 부분 등이 1~2년내 현실화 될 것으로 알려졌다.

다만, 이를 실제 IBM의 컴퓨터 칩셋인 파워 프로세서에 적용하고, 타 반도체 업체에 상용화 할 수 있을때까지는 3~5년 정도의 중장기적인 시간이 필요할 것이라고 샘즈 부사장은 내다봤다.

요크타운(미국)=강은성기자 esther@inews24.com

--comment--

첫 번째 댓글을 작성해 보세요.

댓글 바로가기